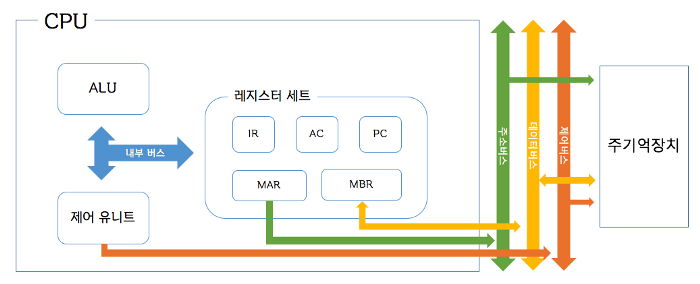

CPU (Central Processing Unit)

- 시스템에 부착된 모든 장치의 동작을 제어하고 명령을 실행하는 장치

- 구조

: 산술논리연산장치(ALU, Arithmetic and Logical Unit)

: 레지스터세트 (Register set)

: 제어유니트(Control Unit)

: 내부 버스 (BUS)

ㆍ데이터 이동을 위한 통로

레지스터 세트

- PC (Program Counter, 프로그램 카운터)

: 다음에 인출될 명령어의 주소를 가지고 있는 레지스터

: A주소의 명령어를 실행 중일 경우 PC내의 값은 A+1

- MAR (Memory Address Register, 메모리 주소 레지스터)

: 프로그램 카운터에 저장된 명령어 주소가 주소 버스로 출력되기 전에 일시적으로 주소를 저장하는 레지스터

- MBR (Memory Buffer Register, 메모리 버퍼 레지스터)

: 기억장치에 저장되거나 읽혀진 데이터를 일시적으로 저장하는 레지스터

- IR (Instruction Register, 명령어 레지스터)

: 가장 최근에 인출된 명령어를 저장하는 레지스터

- AC (Accumulator, 누산기)

: 연산 결과 데이터를 일시적으로 저장하는 레지스터

CPU의 연산

- 메모리에 저장된 명령어들을 순서대로 불러와서 실행하는 과정

- 연산의 종류

: 산술연산 = 사칙연산과 10진수 연산, 고정소수점 연산, 부동소수점 연산

: 논리연산 = 크기 비교 및 참거짓에 대한 논리합, 논리곱 등의 연산

= 논리연산, 시프트, 로테이트, 편집, 변환

- 명령어 수행 단계

1. 인출 (Fetch)

1-1. 프로그램의 메모리 공간에서 명령어를 불러오는 단계

2. 해독 (Decode)

2-1. 불러온 명령어를 해독하여 명령어 내의 데이터 정보와 연산 정보 추출

2-2. CPU내 각 장치에 적절한 제어 신호를 전송하여 연산 및 처리에 대해 준비

3. 실행 (Execute)

3-1. 명령어에서 추출한 데이터와 연상 정보를 이용하여 실제 연산 진행

3-2-1. 메모리 단계로 진행

3-2-2. 연산결과 데이터가 다음 명령어의 입력 데이터로 사용될 경우 라이트 백 단계로 진행

4. 메모리 (Memory)

4-1. 연산결과 데이터를 메모리에 저장

5. 라이트백 (Write-Back)

5-1. 연산결과 데이터를 레지스터에 다시 적재

CPU의 성능 척도

- 클럭 (Clock)

: CPU 내부의 주파수 신호로, 이 신호에 데이터가 동기화 되어 명령어 동작

: ex) 2.0Ghz = 초당 20억개의 명령어 처리 가능

- 코어 (Core)

: CPU의 역할을 수행하는 블럭

: 싱글코어

= 코어가 하나인 형태

= 비용이 저렴하고 프로그래밍이 간단

= 보수작업이나 고장이 발생할 경우 시스템이 멈춤

= 수 많은 작업을 잘 분산시키지 못해 속도가 느림

: 멀티코어

= 여러개의 코어를 병렬적으로 가지는 형태

= 프로그램 작성시 멀티코어를 활용하도록 작성 필요

= 멀티코어의 종류

ㆍ듀얼 / 트리플 / 쿼드 / 헥사 / 옥타 / 데카 / 도데카 / 헥사 데시멀

- MIPS (Million Instruction Per Second)

: 1초 동안 처리할 수 있는 명령의 개수를 100만 단위로 표시

- FLOPS (Floating-point Operations Per Second)

: 1초 동안 처리할 수 있는 부동 소수점 연산의 횟수

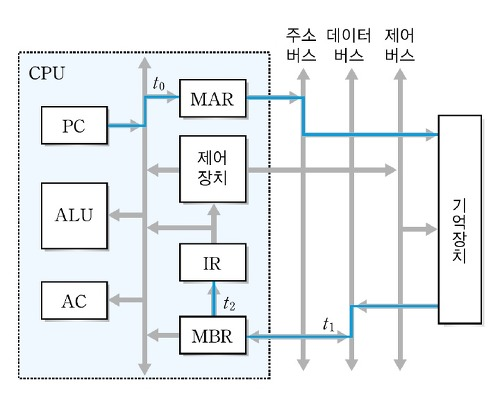

CPU의 명령어 수행과정

Fetch Cycle

1. PC -> MAR

1-1. PC에 저장된 인출될 명령어의 메모리 주소 값을 MAR에 저장

(PC의 데이터를 외부의 주소버스로 전송하기 위해서는 MAR을 거쳐야함)

2. MAR -> MBR

2-1. 버스를 통해 MAR에 저장된 메모리 주소에 접근하여 해당 주소의 데이터를 MBR에 저장

2-2. PC내의 메모리 주소값에 +1

3. MBR -> IR

3-1. MBR내의 데이터를 해석하기 위해 IR로 데이터 전송

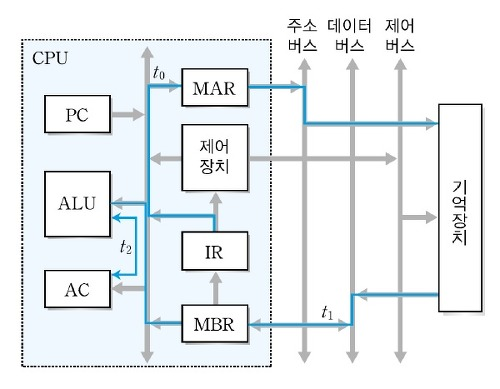

Execute Cycle

1-1. 데이터 이동 (memory)

1-1-1. CPU와 기억장치 및 입출력 장치간 데이터 이동

ex) LOAD addr

1-2. 데이터 처리

1-2-1. 데이터에 대한 산술, 논리연산 수행

ex) STA addr

1-3. 데이터 저장 (write back)

1-3-1. 연산결과 데이터나 입력장치로 부터 읽어들인 데이터를 기억장치에 저장

ex) ADD addr

1-4. 프로그램 제어

1-4-1. 프로그램의 실행순서 결정

ex) JUMP addr

Reference

CPU 명령어 수행 과정

Instruction Cycle = Fetch Cycle + Execute CycleFetch Cycle : 메모리로부터 명령어와 데이터를 processor로 가져오는 단계Execut Cycle : processor가 수행하는 단계Instruction Cycle를 좀

velog.io

2.CPU의 구조와 기능(1)

CPU는 기억장치에 올라와 있는 프로그램의 명령어들을 실행함으로써 프로그램을 수행합니다. 프로그램...

blog.naver.com

[CA/권순재] #2 CPU

스터디 참가자가 스터디를 진행하며 학습한 내용을 정리한 내용입니다.

medium.com

'Computer Science > OS' 카테고리의 다른 글

| CPU - 제어유닛 (Control Unit) (0) | 2021.02.05 |

|---|---|

| CPU - 산술 연산 장치 (ALU)의 구조와 기능 (0) | 2021.02.05 |

| 프로세스와 운영체제 (0) | 2021.02.03 |

| 스레드 (0) | 2021.02.03 |

| 프로세스와 메모리 (0) | 2021.02.03 |